Volume 11 Issue 1, January-March 2023

ISSN: 2995-441X Impact Factor: 7.73

https://kloverjournals.org/journals/index.php/Tech

# STRIKING A BALANCE: NEAREST LEVEL CONTROL TECHNIQUE AND ASYMMETRIC MULTI-LEVEL INVERTER TOPOLOGY FOR VOLTAGE REGULATION IN MODULAR CONVERTERS

# **Rohan Kailash Kapoor**

<sup>1, 2,3</sup>Department of Electrical and Electronics Engineering, Mahatma Gandhi Institute of Technology, Hyderabad, INDIA

**Abstract:** This paper proposes an asymmetric source configuration of multilevel inverter (MLI) topology with Nearest Level Control (NLC) technique for efficient and cost-effective power conversion. The proposed topology consists of eight unidirectional switches, two bidirectional switches, and four isolated DC sources, producing 25-level and 21-level outputs with 1:5 and 1:4 source configurations, respectively. By using NLC technique for switching control, the topology produces both positive and negative voltage levels without the need for a separate backend H-bridge. Moreover, only four switches are in an ON mode in every state, resulting in less per unit Total Standing Voltage and reduced semiconductor device costs.

High-switching frequency Pulse Width Modulation (PWM) techniques often lead to switching losses in high-level inverters. Therefore, this paper proposes the use of NLC technique to reduce switching losses, making it particularly suitable for high-level inverters. The proposed topology has potential applications in renewable energy integration to the grid and drives application. Simulation results obtained using MATLAB/Simulink validate the proposed topology and demonstrate that the inrush current at the input of DC sources has been eliminated.

**Keywords:** Asymmetric source configuration, multilevel inverter, Nearest Level Control, switching losses, renewable energy integration, simulation.

#### **Introduction:**

Multilevel inverters (MLIs) play a significant role in various power conversion applications such as renewable energy integration, motor drives, and power distribution systems. One of the main advantages of MLIs is their ability to produce high-quality output voltage with fewer harmonic distortions. However, the main challenge in the design of MLIs is the requirement of a large number of isolated DC sources and switches, resulting in high cost and complexity.

Several topologies have been proposed to reduce the number of isolated DC sources and switches, such as Cascaded H-Bridge (CHB), Diode-Clamped (DC), and Flying Capacitor (FC) topologies. Among these topologies, the CHB topology is widely used due to its ability to produce a high number of output voltage levels with fewer semiconductor devices. However, the main disadvantage of the CHB topology is its requirement for a large number of isolated DC sources.

To address this issue, this paper proposes an asymmetric source configuration of MLI topology with NLC technique to reduce the number of isolated DC sources and switches, resulting in a cost-effective and efficient power conversion system. The proposed topology produces both positive and negative voltage levels without the need for a separate backend H-bridge.

The NLC technique controls the switching of the proposed topology and reduces switching losses, making it particularly suitable for high-level inverters. The proposed topology has potential applications in renewable energy integration to the grid and drives application. Simulation results

Volume 11 Issue 1, January-March 2023

ISSN: 2995-441X Impact Factor: 7.73

https://kloverjournals.org/journals/index.php/Tech

obtained using MATLAB/Simulink validate the proposed topology and demonstrate that the inrush current at the input of DC sources has been eliminated.

**Proposed Asymmetrical MLI Topology**

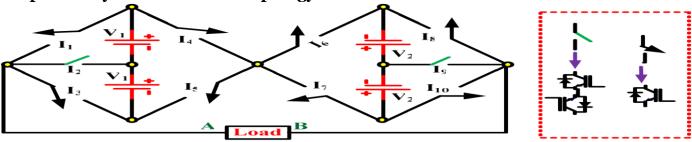

Figure 1. Proposed Asymmetrical MLI topology

The proposed asymmetrical MLI topology is shown in Figure 1. The proposed circuit consists of eight uni-directional switches and two bi-directional switches with four DC sources. With source configuration of 1:5, the peak voltage obtained as  $+12V_{dc}$  and with source configuration of 1:4, the peak voltage obtained is  $+10V_{dc}$ . The switching table for all the voltage levels is shown in Table 1. The proposed topology is simulated in MATLAB/SIMULINK platform and 25-level output has been generated with 1:5 source configuration. Similarly, using the source configuration as 1:4 with same switching action, the 21-level output can be generated. To generate peak output voltage of  $+12V_{dc}$  in 1:5 source configuration topology (i.e  $V_1 = V_{dc}$  and  $V_2 = 5V_1$ ) the switches  $I_1$ ,  $I_5$ ,  $I_7$ ,  $I_8$  are turned ON and remaining switches are OFF, which includes all the DC sources. Similarly, to generate the voltage level of  $+6V_{dc}$  in 1:5 source configuration topology (i.e  $V_1 = V_{dc}$  and  $V_2 = 5V_1$ ) the switches  $I_2$ ,  $I_5$ ,  $I_7$ ,  $I_9$  are turned ON and remaining switches are OFF, which includes only two DC sources. The entire switching action is shown in Table 1, which includes all the voltage levels positive and negative levels from  $+12V_{DC}$  to  $-12V_{DC}$ .

**Table 1**. Switching Table 1:5 source configuration

| S. No | ON State Switches          | Output Voltage      |

|-------|----------------------------|---------------------|

| 1     | $I_2 - I_5 - I_7 - I_{10}$ | 1V <sub>dc</sub>    |

| 2     | $I_1 - I_5 - I_7 - I_{10}$ | 2 V <sub>dc</sub>   |

| 3     | $I_3 - I_4 - I_7 - I_9$    | 3 V <sub>dc</sub>   |

| 4     | $I_2 - I_4 - I_7 - I_9$    | 4 Vdc               |

| 5     | $I_1 - I_4 - I_7 - I_9$    | 5 Vdc               |

| 6     | $I_2 - I_5 - I_7 - I_9$    | 6 Vdc               |

| 7     | $I_1 - I_5 - I_7 - I_9$    | 7 Vdc               |

| S     | $I_3 - I_4 - I_7 - I_8$    | S Vdc               |

| 9     | $I_2 - I_4 - I_7 - I_8$    | 9 Vdc               |

| 10    | $I_1 - I_4 - I_7 - I_8$    | 10 Vdc              |

| 11    | $I_2 - I_5 - I_7 - I_8$    | 11 V <sub>dc</sub>  |

| 12    | $I_1 - I_5 - I_7 - I_8$    | 12 V <sub>dc</sub>  |

| 13    | $I_1 - I_4 - I_6 - I_3$    | 0 V <sub>dc</sub>   |

| 14    | $I_2 - I_4 - I_6 - I_8$    | $-1 V_{dc}$         |

| 15    | $I_3 - I_4 - I_6 - I_8$    | -2 V <sub>dc</sub>  |

| 16    | $I_1 - I_5 - I_6 - I_9$    | -3 V <sub>dc</sub>  |

| 17    | $I_2 - I_5 - I_6 - I_9$    | -4 V <sub>dc</sub>  |

| 18    | $I_1 - I_4 - I_6 - I_9$    | -5 V <sub>dc</sub>  |

| 19    | $I_2 - I_4 - I_6 - I_9$    | -6 V <sub>dc</sub>  |

| 20    | $I_3 - I_4 - I_6 - I_9$    | -7 V <sub>dc</sub>  |

| 21    | $I_1 - I_5 - I_6 - I_{10}$ | -8 V <sub>dc</sub>  |

| 22    | $I_2 - I_5 - I_6 - I_{10}$ | -9 V <sub>dc</sub>  |

| 23    | $I_1 - I_4 - I_6 - I_{10}$ | -10 V <sub>dc</sub> |

| 24    | $I_2 - I_4 - I_6 - I_{10}$ | -11 V <sub>dc</sub> |

| 25    | $I_3 - I_4 - I_6 - I_{10}$ | -12 V <sub>dc</sub> |

#### **NLC scheme**

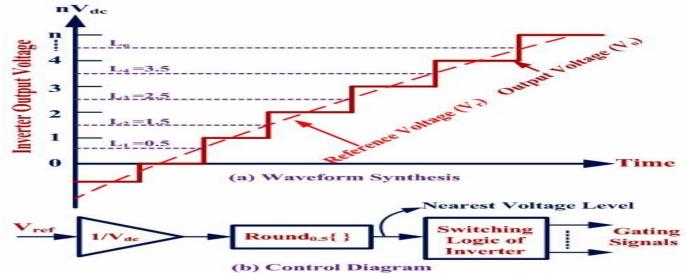

Generally, in any inverter the control scheme plays a vital role and these schemes control the gating signals of the switches. In this paper, the technique called Nearest level Control technique (NLC) is used to generate an output voltage of 25-levels. The scheme is explained with the control diagram and waveform synthesis shown in Figure 2. From the control diagram, it is clear that the reference signal  $V_{\text{ref}}$  (Sinusoidal) is given to the gain block of the value  $V_{\text{dc}}$ . The ratio  $V_{\text{ref}}$  /  $V_{\text{dc}}$  is given to the round function which determines the nearest voltage level from which the switching logic of the

Volume 11 Issue 1, January-March 2023

ISSN: 2995-441X Impact Factor: 7.73

https://kloverjournals.org/journals/index.php/Tech

inverter is derived and given as gating signals to switches. A nearest level control technique is one of important technique preferably used for high level inverters. If the NLC technique is used for low level inverters then it generates lower order harmonics which are quite difficult to eliminate. The waveform synthesis proves that the reference voltage cuts exactly at the midpoint of the staircase waveform as the round $_{0.5}$  {} function is applied.

Figure 2. NLC Scheme Simulation Results

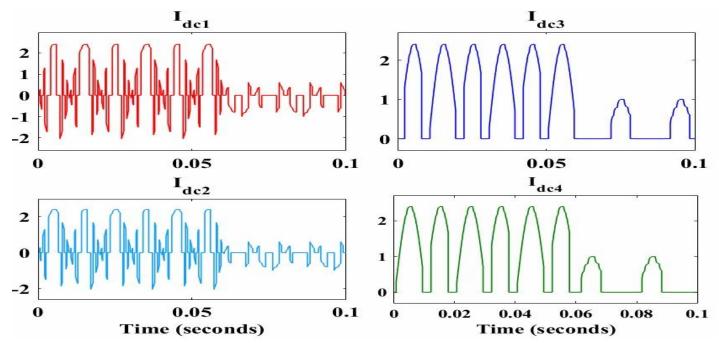

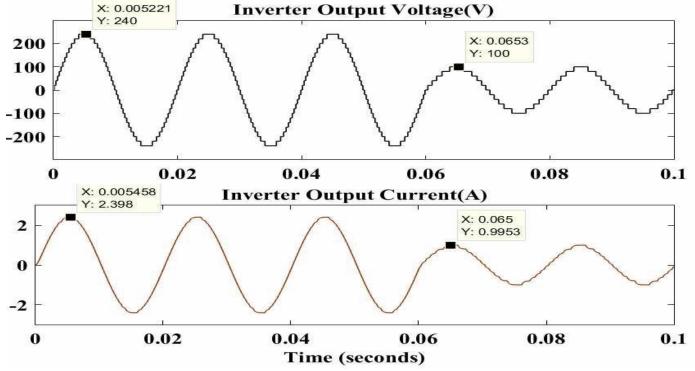

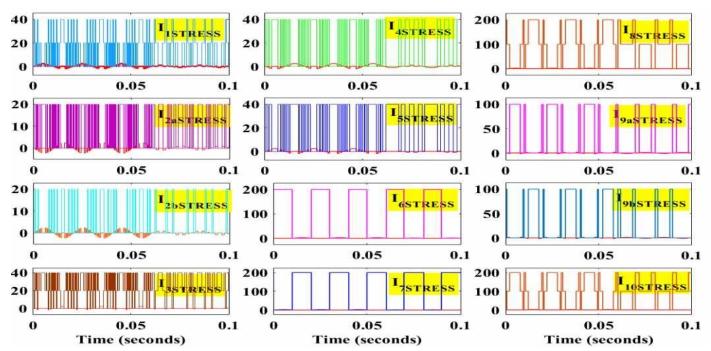

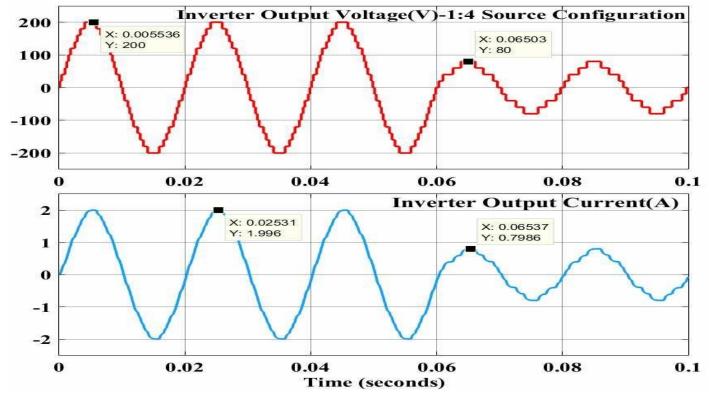

Figure 3 shows the inverter input DC source currents with 1:5 source configuration. The peak value of the current is reduced suddenly if the modulation index is shifted at 0.06s. It is clear from the figure 3 that there are no huge inrush currents at the input of the inverter. Figure 4 shows the inverter output voltage and current. The generated 25- level output with peak value as  $12V_{dc}$  (with  $V_{dc} = 20V$ ) = 240V is shown in figure 4. After the modulation index has been shifted from 1 to 0.4 the inverter generates 11level output with peak value as  $5V_{dc} = 100V$ . The peak inverter output current at modulation index as unity is 2.398 A and at 0.06s the peak value has been reduced to 0.9953 A. The voltage and current stresses of all switches for 1:5 source configuration is shown in figure 5. The 21-level output voltage of the inverter with 1:4 source configuration is shown in figure 6. The peak voltage value of the inverter is +10  $V_{dc}$  = 200V at modulation index as unity. The output levels of the same inverter configuration are reduced to 9 levels at 0.06s when the modulation index is shifted to 0.4 from unity. Now, the peak voltage value of the inverter is +4 $V_{dc}$  = 80 V. Similarly, by referring to the inverter output current waveform from the figure 6, the peak value of the current before 0.06s is 1.996A and after 0.06s the peak current is reduced to 0.7986 A as modulation index is reduced to 0.4. The Simulation parameters are given in Table 3.

Volume 11 Issue 1, January-March 2023

ISSN: 2995-441X Impact Factor: 7.73

https://kloverjournals.org/journals/index.php/Tech

**Figure 3.** Inverter Input DC source currents for 1:5 source configuration with modulation index shifted from 1 to 0.4 at 0.06s

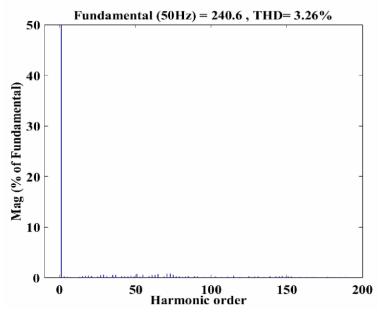

The Comparison of different asymmetrical MLI topologies is shown in Table 2, where 'p' indicates, number of levels. In Hosseinzadeh et al. (2012), the number of IGBTs required is 10log<sup>p</sup>, where 'p' is considered as 17 levels only. The harmonic analysis is shown in figure 7, here at the fundamental frequency the inverter peak output voltage is 240.6V and %THD is 3.26% then it finally meets the IEEE1547 standards

**Figure 4.** Inverter Output voltage and Inverter output current for 1:5 source configuration with modulation index shifted from 1 to 0.4 at 0.06s

Volume 11 Issue 1, January-March 2023

ISSN: 2995-441X Impact Factor: 7.73

https://kloverjournals.org/journals/index.php/Tech

**Figure 5.** Voltage and current stresses of all power semiconductor switches for 1:5 source configuration.

**Figure 6.** Inverter output voltage and Inverter output current for 1:4 source configuration with modulation index shifted from 1 to 0.4 at 0.06sec

Table 2. Comparison of different asymmetrical MLI topologies: Generalized Equations

Volume 11 Issue 1, January-March 2023

ISSN: 2995-441X Impact Factor: 7.73

https://kloverjournals.org/journals/index.php/Tech

| Topologies                  | N <sub>IGBT</sub>                                     | $N_{Driver}$                                          | N <sub>sources</sub>                   | TSV*(V <sub>DC</sub> ) | Negative Levels |

|-----------------------------|-------------------------------------------------------|-------------------------------------------------------|----------------------------------------|------------------------|-----------------|

| Ebrahimi et al. (2012)      | 8log <sub>5</sub> <sup>P</sup>                        | 6log <sub>5</sub> <sup>P</sup>                        | 2log <sub>5</sub> <sup>P</sup>         | 2.75(P-1)              | With H-Bridge   |

| Khosroshahi (2014)          | $3\log_{2}^{P+1} + 1$                                 | $2(\log_2^{P+1} + 1)$                                 | log <sub>2</sub> <sup>P+1</sup> – 1    | 3.667(P-1)             | With H-Bridge   |

| Babaei et al. (2015)        | 5log <sub>2</sub> <sup>P+5</sup> -9                   | 5log <sub>2</sub> <sup>P+5</sup> -9                   | 3log <sub>2</sub> <sup>P+5</sup> -8    | (3.5P-4.5)             | With H-Bridge   |

| Babaei et al. (2014)        | $4\left(\log_3^{\left(p+\frac{1}{2}\right)}+1\right)$ | $4\left(\log_3^{\left(p+\frac{1}{2}\right)}+1\right)$ | $2\log_3^{\left(p+\frac{1}{2}\right)}$ | 3(P-1)                 | With H-Bridge   |

| Babaei (2008)               | $6\log_3^{\left(p+\frac{1}{2}\right)} + 4$            | $3\log_3^{\left(p+\frac{1}{2}\right)} + 4$            | $2\log_3^{\left(p+\frac{1}{2}\right)}$ | 4.5(P-1)               | With H-Bridge   |

| Gupta and Jain (2014)       | $\sqrt{4P-3}+1$                                       | $\sqrt{4P-3}+1$                                       | $0.5(\sqrt{4P-3}-1)$                   | 2(P-1)                 | Inherent        |

| Alishah et al. (2017)       | 10log P                                               | 8log <sup>P</sup> <sub>17</sub>                       | 4log <sup>P</sup> <sub>17</sub>        | 2.5(P-1)               | With H-Bridge   |

| Hosseinzadeh et al. (2012)  | 10log <sup>P</sup> <sub>17</sub>                      | 8log <sub>17</sub>                                    | 4logP <sub>17</sub>                    | 2.5(P-1)               | With H-Bridge   |

| Sharma and Kapoor<br>(2016) | 10log <sup>P</sup> <sub>17</sub>                      | 8log <sub>17</sub>                                    | 4log P 17                              | 2.5(P-1)               | With H-Bridge   |

| Proposed                    | 5log <sub>5</sub> <sup>P</sup>                        | 5log <sub>5</sub> <sup>P</sup>                        | 2log <sub>5</sub> <sup>P</sup>         | 2.5(P-1)               | Inherent        |

**Figure 7.** Harmonic Spectrum of Inverter Output Voltage-25 level output with 1:5 Source Configuration: MI=1.0

Table 3. Simulation Parameters

| S. No | Description           | Value       |

|-------|-----------------------|-------------|

| 1     | V <sub>DC</sub>       | 20V         |

| 2     | R                     | 100 ohms    |

| 3     | L                     | 30mH        |

| 4     | Output Frequency      | 50Hz        |

| 5     | Voltage gain          | 1.0         |

| 6     | Source Configurations | 1:5 and 1:4 |

Volume 11 Issue 1, January-March 2023

ISSN: 2995-441X Impact Factor: 7.73

https://kloverjournals.org/journals/index.php/Tech

| 7 | Modulation Index | 1 to 0.4 |

|---|------------------|----------|

| 8 | TSV (p.u)        | 5.0      |

#### **Conclusion**

In this paper, a new asymmetrical MLI topology with two types of source configurations has been proposed and which requires less switch count when compared with other conventional topologies. The cost requirement of the switching devices can become reduces since less per unit TSV value is obtained. Basically, the reduction of switch count indicates that the respective reduction in gate drive circuits, heat sink and protection circuits. The NLC technique is used to provide the gate pulses to the switches which reduces switching losses and %THD value greatly reduces as compared with other conventional PWM control techniques. The change in peak value of the inverter output voltage and output current is observed with the step change of modulation index values from 1 to 0.4. The %THD value obtained for 25-level inverter output voltage with 1:5 source configuration is 3.26% and finally it meets the requirement of IEEE standards. The drawback of this topology is that it does not provide any boosting ability since voltage gain as unity. This topology is well suitable for grid connected applications.

#### References

- Alishah R.S., Hosseini S.H., Babaei E. and Sabahi M., 2017, Optimal design of new cascaded switch-ladder multilevel inverter structure, in *IEEE Transactions on Industrial Electronics*, Vol. 64, No. 3, pp. 2072-2080. https://doi.org/10.1109/TIE.2016.2627019.

- Babaei E., Laali S. and Bayat Z., 2015, A single-phase cascaded multilevel inverter based on a new basic unit with reduced number of power switches, in *IEEE Transactions on Industrial Electronics*, Vol. 62, No. 2, pp. 922-929, https://doi.org/10.1109/TIE.2014.2336601.

- Babaei E., Farhadi-Kangarlu M., Sabahi M., 2014, Extended multilevel converters: an attempt to reduce the number of independent DC voltage sources in cascaded multilevel converters. *IET Power Electronics*, Vol. 7, pp. 157-166. https://doi.org/10.1049/iet-pel.2013.0057

- Babaei E., 2008, A cascade multilevel converter topology with reduced number of switches, in *IEEE Transactions on Power Electronics*, Vol. 23, No. 6, pp. 2657-2664. https://doi.org/10.1109/TPEL.2008.2005192.

- Bana P.R., Panda K.P., Naayagi R.T., Siano P. and Panda G., 2019, Recently developed reduced switch multilevel inverter for renewable energy integration and drives application: topologies, comprehensive analysis and comparative evaluation, in *IEEE Access*, Vol. 7, pp. 54888-54909. https://doi.org/10.1109/ACCESS.2019.2913447.

- Bhanuchandar and Murthy B. K., 2021, Single phase nine level switched capacitor based grid connected inverter with LCL filter, 2020 3rd International Conference on Energy, Power and Environment: Towards Clean Energy Technologies, pp. 1-5, https://doi.org/10.1109/ICEPE50861.2021.9404491

- Ebrahimi J., Babaei E. and Gharehpetian G.B., 2012, A new multilevel converter topology with reduced number of power electronic components, in *IEEE Transactions on Industrial Electronics*, Vol. 59, No. 2, pp. 655-667. https://doi.org/10.1109/TIE.2011.2151813

Volume 11 Issue 1, January-March 2023

ISSN: 2995-441X Impact Factor: 7.73

https://kloverjournals.org/journals/index.php/Tech

- Gupta K.K. and Jain S. 2014, Comprehensive review of a recently proposed multilevel inverter. *IET Power Electronics*, Vol. 7, pp. 467-479. https://doi.org/10.1049/iet-pel.2012.0438

- Gupta K. K., Ranjan A., Bhatnagar P., Sahu L.K. and Jain S., 2016, Multilevel inverter topologies with reduced device count: a review, in *IEEE Transactions on Power Electronics*, Vol. 31, No. 1, pp. 135-151. https://doi.org/10.1109/TPEL.2015.2405012.

- Hosseinzadeh M.A., Babaei E. and Sabahi M., 2012, Back-to-back stacked multicell converter, 2012 3rd Power Electronics and Drive Systems Technology (PEDSTC), pp. 410-415. https://doi.org/10.1109/PEDSTC.2012.6183365

- Khosroshahi, M.T. 2014, Crisscross cascade multilevel inverter with reduction in number of components. IET Power Electronics, Vol. 7, pp. 2914-2924. https://doi.org/10.1049/iet-pel.2013.0541

- Kumar K.B., Bhanuchandar A. and Mahesh C., 2021, A novel control scheme for symmetric seven level reduced device count multi-level DC link (MLDCL) inverter, *2021 International Conference on Sustainable Energy and Future Electric Transportation (SEFET)*, pp. 1-4. https://doi.org/10.1109/SeFet48154.2021.9375714.

- Meshram P.M. and Borghate V.B., 2015, A simplified nearest level control (NLC) voltage balancing method for modular multilevel converter (MMC), in *IEEE Transactions on Power Electronics*, Vol. 30, No. 1, pp. 450-462. https://doi.org/10.1109/TPEL.2014.2317705

- Pereda J. and Dixon J., 2012, 23-level inverter for electric vehicles using a single battery pack and series active filters, in *IEEE Transactions on Vehicular Technology*, Vol. 61, No. 3, pp. 1043-1051. https://doi.org/10.1109/TVT.2012.2186599

- Rodriguez J., Lai J.-S. and Peng F.Z., 2002, Multilevel inverters: a survey of topologies, controls, and applications, in *IEEE Transactions on Industrial Electronics*, Vol. 49, No. 4, pp. 724-738. https://doi.org/10.1109/TIE.2002.801052.

- Sharma G. and Kapoor A.K., 2016, A dynamic voltage restorer based on voltage balanced back-to-back stacked multicell converter with equal voltage sources, *2016 IEEE Region 10 Conference* (*TENCON*), pp. 2930-2934. https://doi.org/10.1109/TENCON.2016.7848581

- Su G.-J., 2005, Multilevel DC-link inverter, in *IEEE Transactions on Industry Applications*, Vol. 41, No. 3, pp. 848-854. https://doi.org/10.1109/TIA.2005.847306.

- Vijeh M., Rezanejad M., Samadaei E. and Bertilsson K., 2019, A general review of multilevel inverters based on main submodules: structural point of view, in *IEEE Transactions on Power Electronics*, Vol. 34, No. 10, pp. 9479-9502.https://doi.org/10.1109/TPEL.2018.2890649.